During the IMAPS Conference and Exhibit in San Diego last month, one of the topics mentioned over and over again was coplanarity in die bonding.

It appears that this topic continues to come up more frequently because of 2.5 and 3D chip stacking. Performance of such vertically integrated devices relies on co-planar surfaces that successfully make contact with all pads/pillars. That being said, there are very specific variables involved in finding solutions for optimizing planarity….both for large and smaller die. Especially in die stacking and copper pillar processes, bonding two surfaces and ensuring they are coplanar is essential.

1. Bonding without parallelism compensation

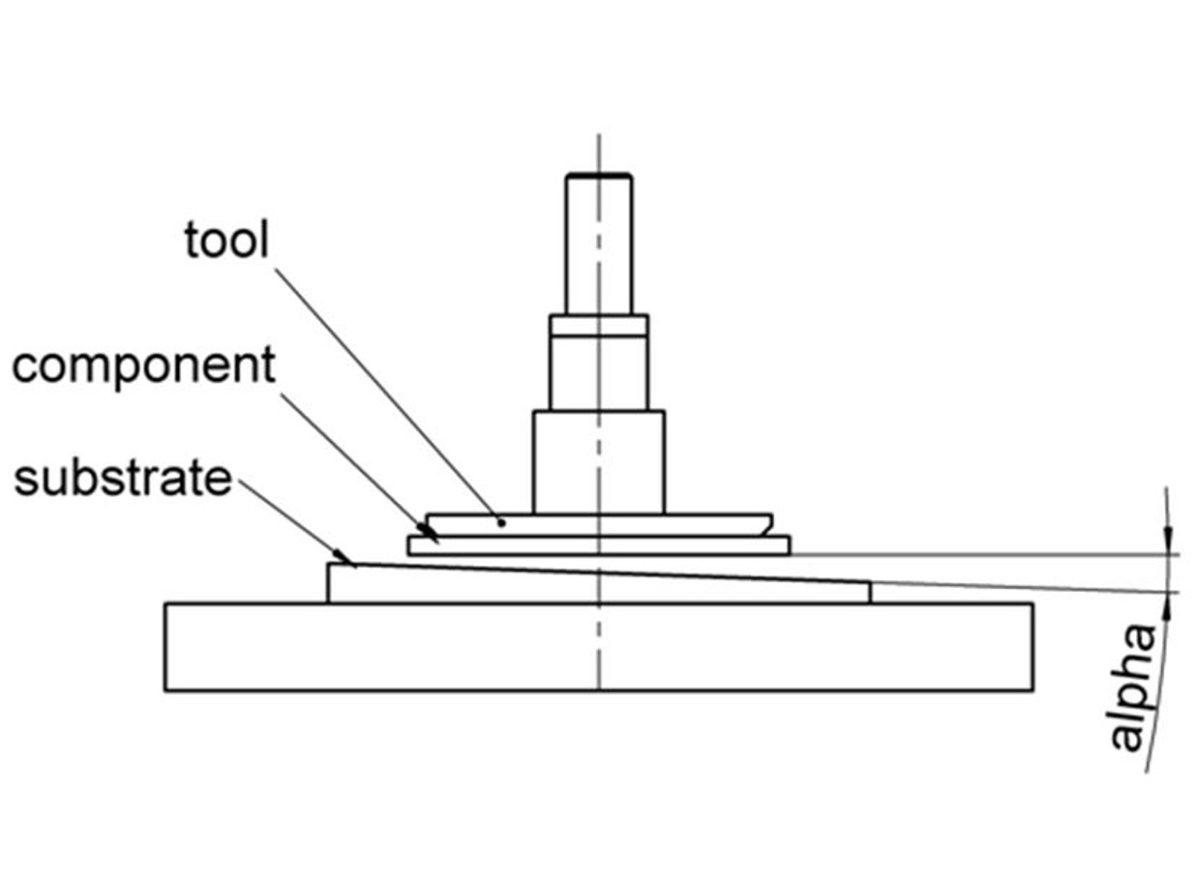

Fixed tools do not have any means of adjustment for individual parallelism. Components are bonded without any further intervention. The achievable coplanarity depends on the basic settings (mechanical) of the placement system. The fixed aspect can result in higher stability, repeatability and accuracy but a fixed tool does not have the capability to make adjustments if necessary.

2. Bonding with active parallelism compensation

Bonding with a tool that includes active parallelism compensation allows components to be adjusted by actuators to achieve coplanarity. The precision in determining the gaps and resolution of the actuators influence the result. This can be a very expensive and unnecessary method. Unless the resolution is sub-micron, it begs the question, what’s the point?

3. Bonding with passive parallelism compensation

With Finetech’s technology, components are aligned by contact with the substrate (or a reference surface) with free movement of a unique placement tool. As a die is placed onto the substrate, or one chip is placed on top of another chip, the placement tool is able to adjust its position in all axis. This allows the die to be coplanar to the substrate – as long as the chip and die are relatively flat already (>0.5mm).

We are moving into the world of vertically integrated devices. Mobile devices are being designed with miniaturized and denser electronics, so we find ways to cram more stuff inside. Die to die interconnect, multichip modules, etc., will continue to push the envelope. We welcome any questions you may have on coplanarity… it deals with accuracy, and that’s what we do!

11/29/2014, created by: Robert Avila